# Introduction to Advanced System-on-Chip Test Design and Optimization

Erik Larsson

# INTRODUCTION TO ADVANCED SYSTEM-ON-CHIP TEST DESIGN AND OPTIMIZATION

#### FRONTIERS IN ELECTRONIC TESTING

**Books** in the series:

#### Consulting Editor Vishwani D. Agrawal

Embedded Processor-Based Self-Test D. Gizopoulos ISBN: 1-4020-2785-0 **Testing Static Random Access Memories** S. Hamdioui ISBN: 1-4020-7752-1 Verification by Error Modeling K. Radecka and Zilic ISBN: 1-4020-7652-5 Elements of STIL: Principles and Applications of IEEE Std. 1450 G. Maston, T. Taylor, J. Villar ISBN: 1-4020-7637-1 Fault Injection Techniques and Tools for Embedded systems Reliability Evaluation A. Benso, P. Prinetto ISBN: 1-4020-7589-8 High Performance Memory Memory Testing R. Dean Adams ISBN: 1-4020-7255-4 SOC (System-on-a-Chip) Testing for Plug and Play Test Automation K. Chakrabarty ISBN: 1-4020-7205-8 Test Resource Partitioning for System-on-a-Chip K. Chakrabarty, Iyengar & Chandra ISBN: 1-4020-7119-1 A Designers' Guide to Built-in Self-Test C. Stroud ISBN: 1-4020-7050-0 **Boundary-Scan Interconnect Diagnosis** J. de Sousa, P.Cheung ISBN: 0-7923-7314-6 Essentials of Electronic Testing for Digital, Memory, and Mixed Signal VLSI Circuits M.L. Bushnell, V.D. Agrawal ISBN: 0-7923-7991-8 Analog and Mixed-Signal Boundary-Scan: A Guide to the IEEE 1149.4 Test Standard A. Osseiran ISBN: 0-7923-8686-8 Design for At-Speed Test, Diagnosis and Measurement B. Nadeau-Dosti ISBN: 0-79-8669-8 **Delay Fault Testing for VLSI Circuits** A. Krstic, K-T. Cheng ISBN: 0-7923-8295-1 Research Perspectives and Case Studies in System Test and Diagnosis J.W. Sheppard, W.R. Simpson ISBN: 0-7923-8263-3 Formal Equivalence Checking and Design Debugging S.-Y. Huang, K.-T. Cheng ISBN: 0-7923-8184-X **Defect Oriented Testing for CMOS Analog and Digital Circuits** M. Sachdev ISBN: 0-7923-8083-5

# INTRODUCTION TO ADVANCED SYSTEM-ON-CHIP TEST DESIGN AND OPTIMIZATION

by

ERIK LARSSON Linköpings University, Sweden

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN-10 1-4020-3207-2 (HB) Springer Dordrecht, Berlin, Heidelberg, New York ISBN-10 0-387-25624-5 (e-book) Springer Dordrecht, Berlin, Heidelberg, New York ISBN-13 978-1-4020-3207-3 (HB) Springer Dordrecht, Berlin, Heidelberg, New York ISBN-13 978-0-387-25624-5 (e-book) Springer Dordrecht, Berlin, Heidelberg, New York

Published by Springer, P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

Printed on acid-free paper

All Rights Reserved © 2005 Springer No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed in the Netherlands.

# Contents

| Pref | ace  |        |           |                                   | xiii |

|------|------|--------|-----------|-----------------------------------|------|

| Acl  | knov | vledge | ements    |                                   | xvii |

| Part | 1    | Testir | ng conce  | pts                               |      |

| 1.   | IN   | TROI   | DUCTIO    | Ň                                 | 1    |

| 2.   | DI   | ESIGN  | J FLOW    |                                   | 5    |

|      | 1    | Intro  | oduction  |                                   | 5    |

|      | 2    | High   | n-level d | esign                             | 6    |

|      | 3    | U      | e-Based   | e                                 | 7    |

|      | U    |        |           | rk-on-Chip                        | 9    |

|      |      |        |           | m-Based Design                    | 9    |

|      | 4    | Cloc   | king      | -                                 | 10   |

|      |      |        | U         | 1 Timing                          | 11   |

|      |      |        | •         | Distribution                      | 11   |

|      |      | 4.3    | Multip    | le Clock Domains                  | 12   |

|      |      |        | 4.3.1     |                                   | 12   |

|      |      |        | 4.3.2     |                                   | 13   |

|      | 5    | Opti   | mizatior  | 1                                 | 14   |

|      |      | 5.1    | Optimi    | zation Techniques                 | 16   |

|      |      |        | 5.1.1     | Backtracking and Branch-and-bound | 16   |

|      |      |        | 5.1.2     |                                   | 17   |

|      |      |        | 5.1.3     |                                   | 17   |

|      |      |        | 5.1.4     | Simulated Annealing               | 18   |

|      |      |        | 5.1.5     | e e                               | 18   |

|      |      |        | 5.1.6     | Tabu Search                       | 19   |

|      |      |        |           |                                   |      |

| 3. | DF | ESIGN                   | I FOR TH  | EST                                    | 21 |

|----|----|-------------------------|-----------|----------------------------------------|----|

|    | 1  | Intro                   | oduction  |                                        | 21 |

|    |    | 1.1                     | Fault m   | odels                                  | 21 |

|    |    |                         | 1.1.1     | Stuck-at Fault Model                   | 22 |

|    |    |                         | 1.1.2     | Bridging Fault Model                   | 22 |

|    |    |                         | 1.1.3     |                                        | 23 |

|    |    |                         | 1.1.4     | Delay Fault Model                      | 23 |

|    |    | 1.2                     | Test Ge   | eneration for Combinational Circuits   | 24 |

|    |    |                         | 1.2.1     | Path Sensitization                     | 25 |

|    |    |                         | 1.2.2     | Boolean Difference                     | 25 |

|    |    |                         | 1.2.3     | D-algorithm                            | 26 |

|    |    |                         | 1.2.4     | PODEM (Path-Oriented Decision-Making)  | 27 |

|    |    |                         | 1.2.5     | FAN (Fanout-Oriented Test Generation)  | 28 |

|    |    |                         | 1.2.6     | Subscripted D-Algorithm                | 28 |

|    |    |                         | 1.2.7     | CONcurrent Test Generation             | 28 |

|    |    |                         | 1.2.8     | Fault Simulation                       | 28 |

|    |    |                         | 1.2.9     | Optimization                           | 28 |

|    |    |                         | 1.2.10    | Delay Fault Detection                  | 30 |

|    |    | 1.3                     | Testing   | Sequential Circuits                    | 30 |

|    | 2  | Design-for-Test Methods |           |                                        | 31 |

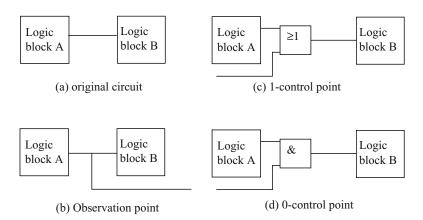

|    |    | 2.1                     | Test Po   | int Insertion                          | 32 |

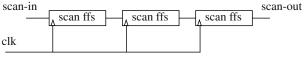

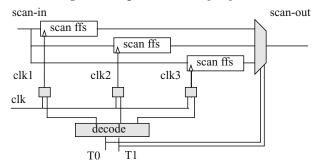

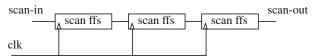

|    |    | 2.2                     | The Sca   | an Technique                           | 32 |

|    |    |                         | 2.2.1     | Scan Testing for Delay Faults          | 36 |

|    |    | 2.3                     | Test Par  | ttern Generation for BIST              | 39 |

|    |    |                         | 2.3.1     | Exhaustive Pattern Generation          | 40 |

|    |    |                         | 2.3.2     | Pseudo-Random Pattern Generation       | 40 |

|    |    |                         | 2.3.3     | Pseudo-random-based test generation    | 40 |

|    |    |                         | 2.3.4     |                                        | 41 |

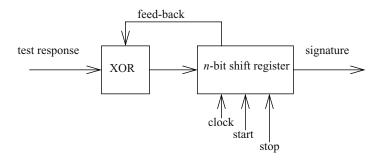

|    |    | 2.4                     | Test Re   | sponse Analysis for BIST               | 41 |

|    |    | 2.5                     | Circular  | r-BIST                                 | 43 |

|    |    | 2.6                     | BIST-A    | rchitectures                           | 43 |

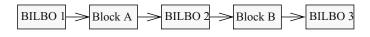

|    |    |                         | 2.6.1     | BILBO (Built-In Logic Block Observer), | 43 |

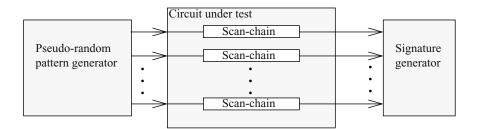

|    |    |                         | 2.6.2     | STUMPS Architecture                    | 44 |

|    |    |                         | 2.6.3     | LOCST (LSSD On-Chip Self-Test)         | 44 |

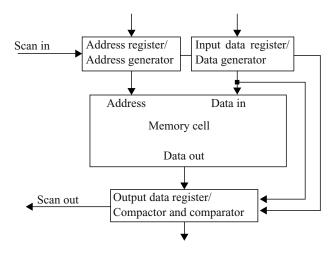

|    |    | 2.7                     | Memor     | y Testing                              | 45 |

|    |    |                         | 2.7.1     | Algorithmic Test Sequence (ATS)        | 48 |

|    |    |                         | 2.7.2     | Marching Pattern Sequences (MARCH)     | 48 |

|    |    |                         | 2.7.3     | Checkboard Test                        | 49 |

|    |    |                         | 2.7.4     | Memory BIST                            | 49 |

|    |    |                         | 2.7.5     | Memory Diagnosis and Repair            | 50 |

|    | 3  | Mix                     | ed-Signal | l Testing                              | 51 |

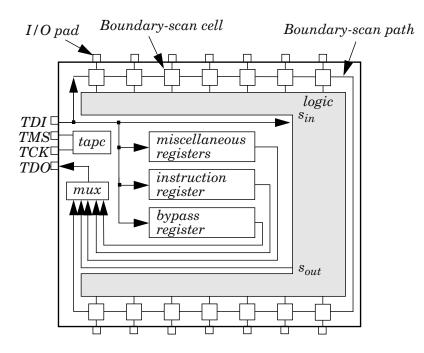

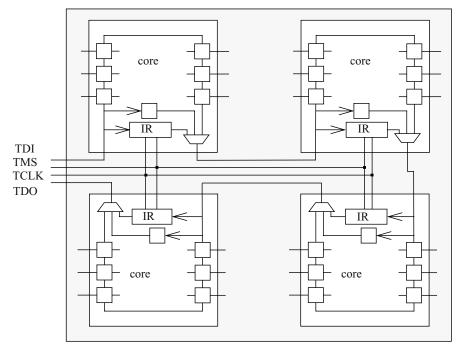

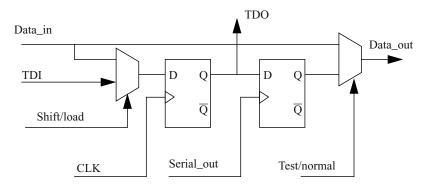

| 4.  | BC  | DUNDARY SCAN                                                                                                                               | 53                   |

|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|     | 1   | Introduction                                                                                                                               | 53                   |

|     | 2   | <ul> <li>The Boundary-Scan Standards (IEEE 1149.1)</li> <li>2.1 Registers</li> <li>2.2 TAP Controller</li> <li>2.3 Instructions</li> </ul> | 53<br>56<br>57<br>57 |

|     |     | <ul><li>2.3.1 Example</li><li>2.3.2 Boundary-Scan Languages</li><li>2.3.3 Cost of Boundary Scan</li></ul>                                  | 57<br>58<br>58       |

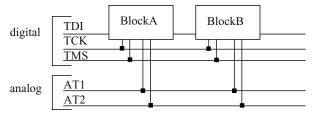

|     | 3   | Analog Test Bus (IEEE 1149.4)                                                                                                              | 61                   |

|     | -   | 3.1 Analog Test Access Port (ATAP)                                                                                                         | 63                   |

|     |     | 3.2 Test Bus Interface Circuit (TBIC)                                                                                                      | 63                   |

|     |     | 3.3 Analog Boundary Module (ABM)                                                                                                           | 63                   |

|     |     | 3.4 Instructions                                                                                                                           | 63                   |

|     |     | 3.5 Chaining Example                                                                                                                       | 63                   |

| Par | t 2 | SOC Design for Testability                                                                                                                 |                      |

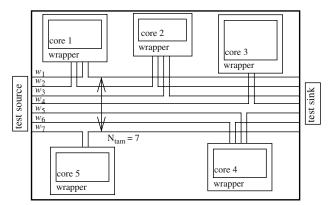

| 5.  | SY  | STEM MODELING                                                                                                                              | 67                   |

|     | 1   | Introduction                                                                                                                               | 67                   |

|     | 2   | Core modeling                                                                                                                              | 68                   |

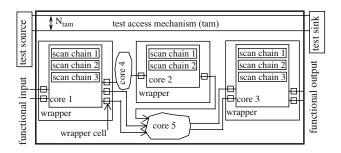

|     | 3   | Test Resource modeling                                                                                                                     | 71                   |

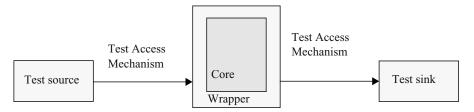

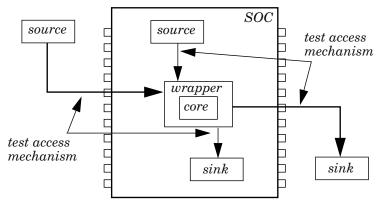

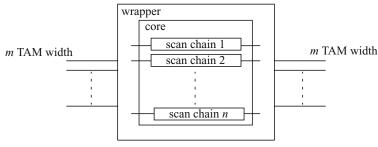

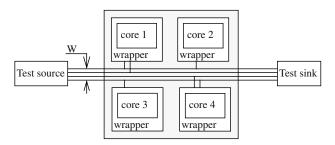

|     | 4   | Core Wrapper                                                                                                                               | 72                   |

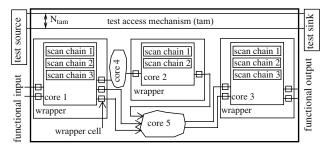

|     | 5   | Test Access Mechanism                                                                                                                      | 74                   |

| 6.  | TE  | EST CONFLICTS                                                                                                                              | 77                   |

|     | 1   | Introduction                                                                                                                               | 77                   |

|     | 2   | Limitations at the Tester                                                                                                                  | 78                   |

|     |     | 2.1 Bandwidth Limitations                                                                                                                  | 79                   |

|     |     | 2.2 Tester Memory Limitations                                                                                                              | 79                   |

|     |     | 2.3 Test Channel Clocking                                                                                                                  | 80                   |

|     | 3   | Test Conflicts                                                                                                                             | 81                   |

|     |     | 3.1 General Test Conflicts                                                                                                                 | 81                   |

|     |     | 3.2 Multiple Test Set                                                                                                                      | 82                   |

|     |     | <ul><li>3.3 Multiple Sets of Test Sets</li><li>3.4 Interconnection Testing - Cross-Core Testing</li></ul>                                  | 82<br>84             |

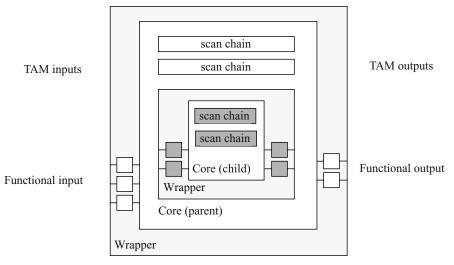

|     |     | 3.5 Hierarchy - Cores Embedded in Cores                                                                                                    | 85                   |

|     | 4   | Discussion                                                                                                                                 | 86                   |

|     | •   | ·· ···                                                                                                                                     | 50                   |

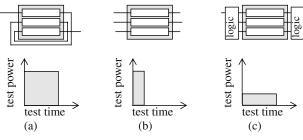

| 7. | TE | EST POWER DISSIPATION                                                                           | 89         |

|----|----|-------------------------------------------------------------------------------------------------|------------|

|    | 1  | Introduction                                                                                    | 89         |

|    | 2  | Power consumption                                                                               | 90         |

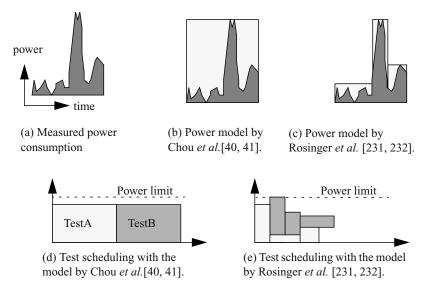

|    | 3  | System-level Power modeling                                                                     | 91         |

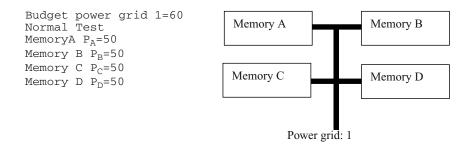

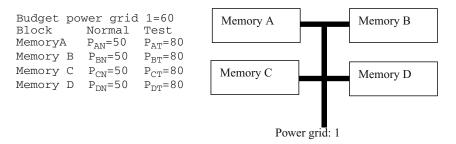

|    | 4  | Hot-spot modeling with Power Grids                                                              | 93         |

|    | 5  | Core-level Power modeling                                                                       | 95         |

|    | 6  | Discussion                                                                                      | 98         |

| 8. | TE | EST ACCESS MECHANISM                                                                            | 99         |

|    | 1  | Introduction                                                                                    | 99         |

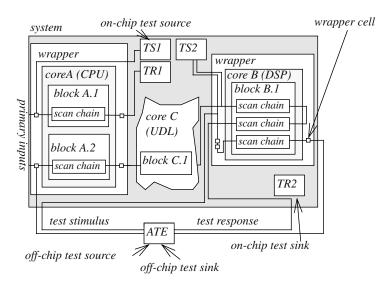

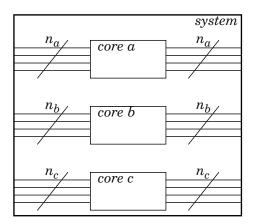

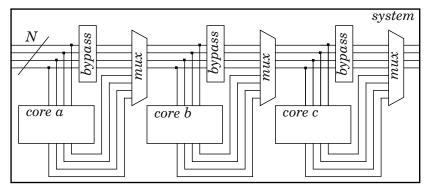

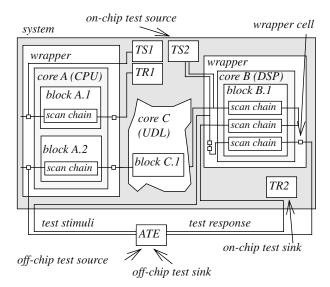

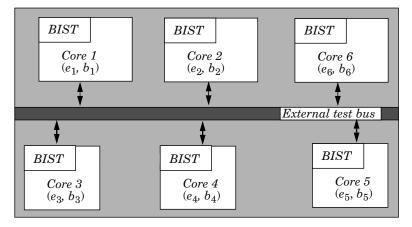

|    |    | 1.1 System-on-Chip Test Data Transportation                                                     | 100        |

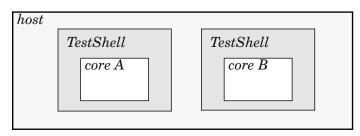

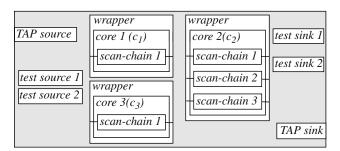

|    |    | 1.1.1 The TestShell and P1500 Approach                                                          | 100        |

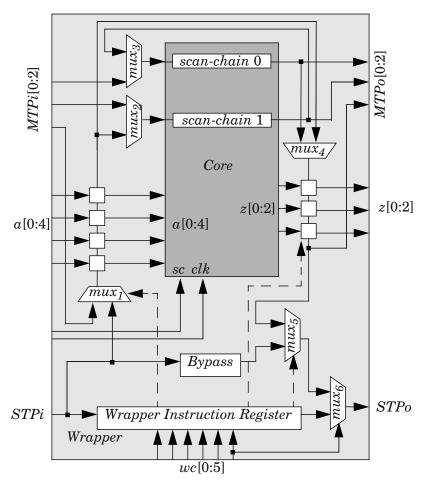

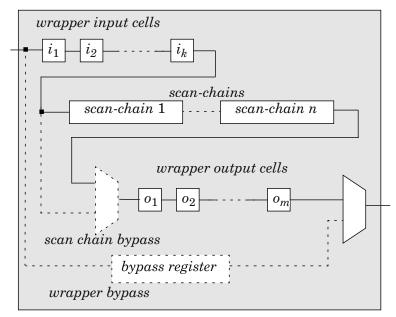

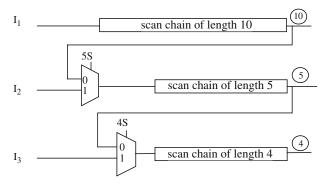

|    |    | 1.2 Reconfigurable Core Wrappers                                                                | 106        |

|    | 2  | Test Access Mechanism Design                                                                    | 107        |

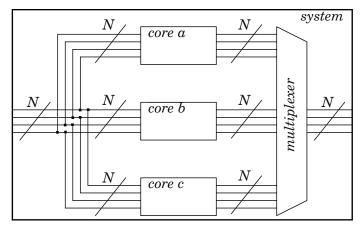

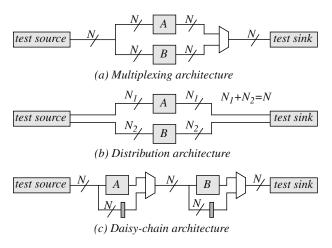

|    |    | 2.1 Multiplexing Architecture                                                                   | 108        |

|    |    | 2.2 Distribution Architecture                                                                   | 109        |

|    |    | <ul><li>2.3 Daisychain Architecture</li><li>2.4 Test Bus Architecture</li></ul>                 | 110<br>111 |

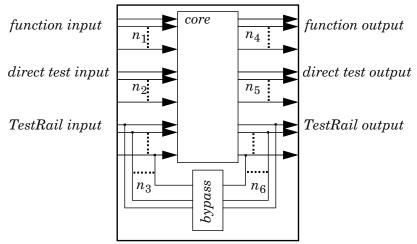

|    |    | 2.4 Test Bus Architecture<br>2.5 TestRail Architecture                                          | 111        |

|    |    | 2.6 Flexible-Width Architecture                                                                 | 112        |

|    |    | 2.7 Core Transparancy                                                                           | 112        |

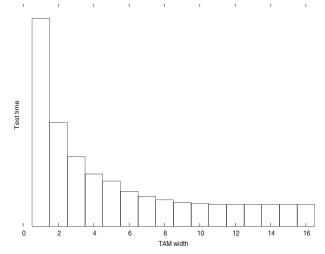

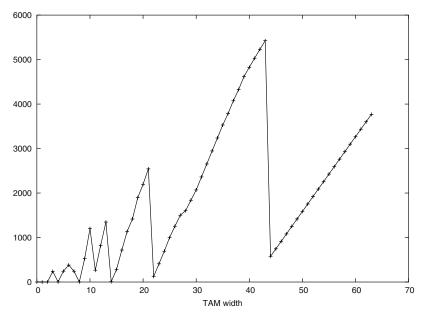

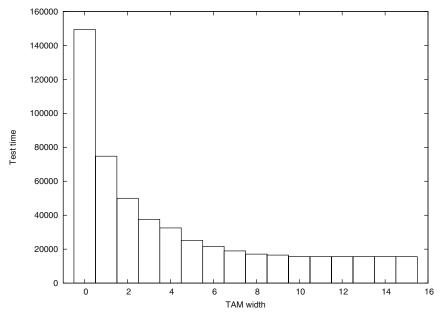

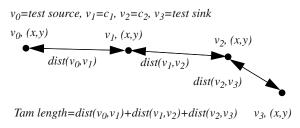

|    | 3  | Test TIME Analysis                                                                              | 113        |

| 9. | TE | EST SCHEDULING                                                                                  | 115        |

|    | 1  | Introduction                                                                                    | 115        |

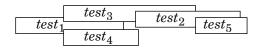

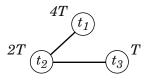

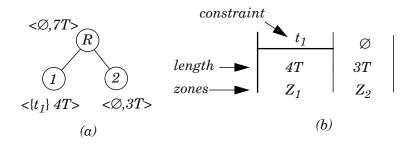

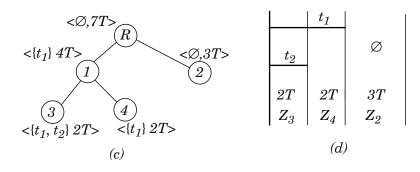

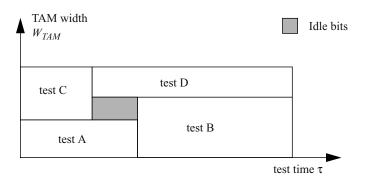

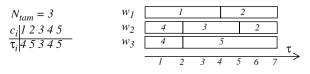

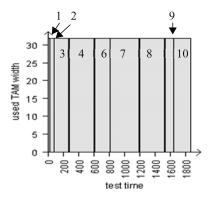

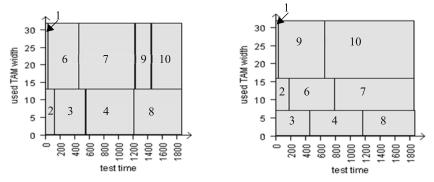

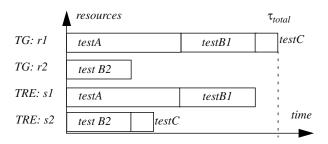

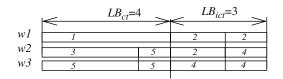

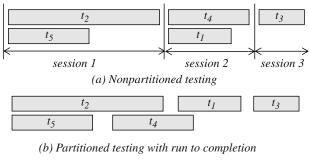

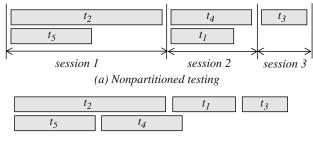

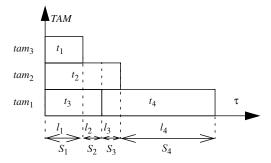

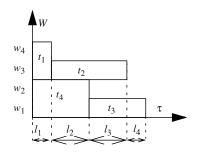

|    | 2  | scheduling of Tests with fixed test time under test conflicts<br>2.1 Preemptive test scheduling | 119<br>128 |

|    | 3  | scheduling of tests with non-fixed (variable) testing times                                     | 128        |

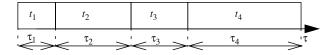

|    | -  | 3.1 Idle Types                                                                                  | 128        |

|    |    | 3.1.1 Imbalanced TAM Test Completion Times                                                      | 129        |

|    |    | 3.1.2 Module Assigned to TAM of Non Pareto Opt                                                  | imal       |

|    |    | Width                                                                                           | 130        |

|    |    | 3.1.3 Imbalanced Scan Chains in Module                                                          | 131        |

|    |    | 3.1.4 Other Types of Idle Bits                                                                  | 131        |

|    |    | 3.2 SOC Test Scheduling with Fixed-Width TAM                                                    | 132        |

|    |    | 3.3 SOC Test Scheduling with Flexible-Width TAM                                                 | 134        |

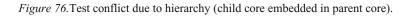

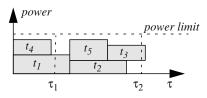

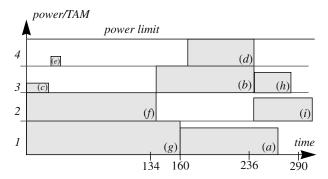

|    |    | 3.3.1 Test Power                                                                                | 137        |

|    |    | 3.3.2 Multiple Test Sets                                                                        | 138        |

|   | 3.4   | Other Test Scheduling Techniques               | 138 |

|---|-------|------------------------------------------------|-----|

|   |       | 3.4.1 Problem: Control lines and Layout.       | 138 |

|   |       | 3.4.2 Problem: Power Modeling                  | 138 |

|   |       | 3.4.3 Problem: Fixed Test Resources            | 139 |

|   |       | 3.4.4 Problem: Multiple Clock Domains          | 140 |

|   |       | 3.4.5 Problem: Delay Fault Testing             | 140 |

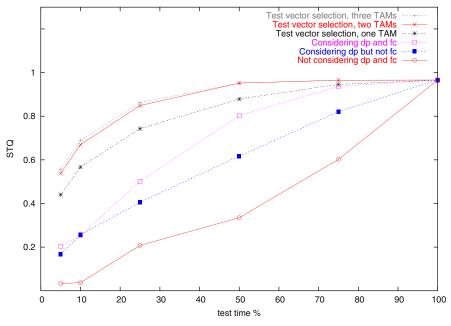

|   |       | 3.4.6 Defect-Oriented Scheduling               | 140 |

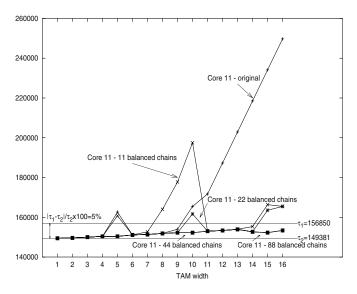

| 4 | Opti  | mal Test time?                                 | 143 |

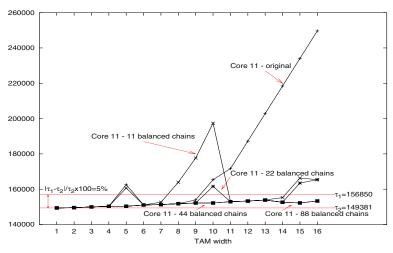

|   | 4.1   | Soft Cores - No Fixed Scan-chains              | 146 |

|   | 4.2   | Hard Cores - Fixed Number of Scan-chains       | 150 |

| 5 | Integ | grated Test Scheduling and TAM Design          | 151 |

|   | 5.1   | Test Time and Test Power Consumption           | 152 |

|   | 5.2   | Bandwidth Assignment                           | 152 |

|   | 5.3   | Test Scheduling                                | 153 |

|   | 5.4   | TAM Planning                                   | 154 |

|   | 5.5   | TAM Optimization                               | 156 |

| 6 | Integ | grating Core Selection in the Test Design Flow | 157 |

| 7 | Furt  | her Studies                                    | 160 |

|   | 7.1   | Combined Test Time and TAM Design Minimization | 160 |

|   | 7.2   | Core Selection in the Test Design Flow         | 160 |

|   | 7.3   | Defect-Oriented Test Scheduling                | 160 |

|   |       |                                                |     |

### Part 3 SOC Test Applications

# 10. A RECONFIGURABLE POWER-CONSCIOUS CORE WRAPPER AND ITS APPLICATION TO SYSTEM-ON-CHIP TEST SCHEDULING 163

| 1 | Introduction                                    | 163 |  |  |

|---|-------------------------------------------------|-----|--|--|

| 2 | Background and Related Work                     | 165 |  |  |

| 3 | A Reconfigurable Power-Conscious Core Wrapper   | 167 |  |  |

| 4 | Optimal Test Scheduling                         | 170 |  |  |

|   | 4.1 Optimal Scheduling of Core Tests            | 171 |  |  |

|   | 4.2 Transformations for Optimal TAM Utilization | 173 |  |  |

|   | 4.3 Cross-Core Test Scheduling                  | 175 |  |  |

|   | 4.4 Optimal Power-Constrained Scheduling        | 177 |  |  |

|   | 4.5 Minimization of TAM Wiring                  | 179 |  |  |

| 5 | Experimental Results                            | 180 |  |  |

| 6 | Conclusions 18                                  |     |  |  |

|   |                                                 |     |  |  |

| 11. | ٨N | I INT      | EGRATED FRAMEWORK FOR THE DESIGN AND OF                             | PTI-       |

|-----|----|------------|---------------------------------------------------------------------|------------|

|     | M  | [ZAT]      | ION OF SOC TEST SOLUTIONS                                           | 187        |

|     | 1  | Intro      | oduction                                                            | 187        |

|     | 2  | Rela       | ated Work                                                           | 188        |

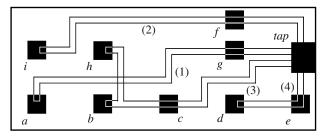

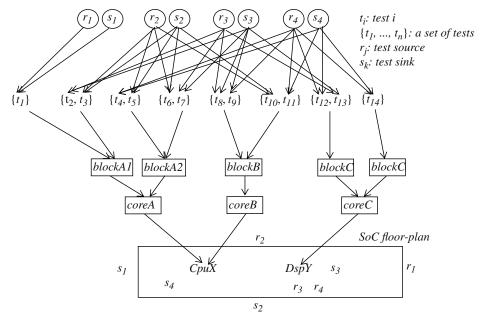

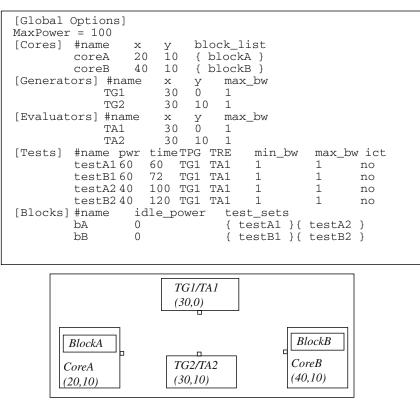

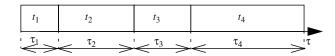

|     | 3  | Syst       | em modeling                                                         | 192        |

|     | 4  | The        | SOC Test Issues                                                     | 194        |

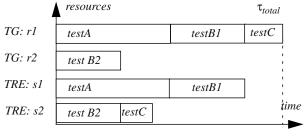

|     |    | 4.1        | Test Scheduling                                                     | 194        |

|     |    | 4.2        | Power Consumption                                                   | 195        |

|     |    | 4.3        | Test Source Limitations                                             | 197        |

|     |    |            | Test Set Selection                                                  | 197        |

|     |    |            | Test Access Mechanism                                               | 198        |

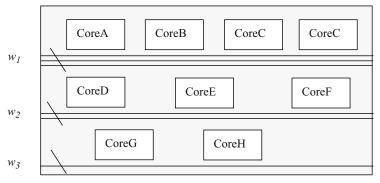

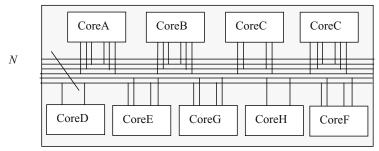

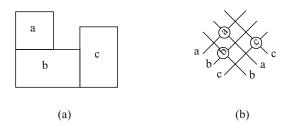

|     |    | 4.6        | Test Floor-planning                                                 | 200        |

|     | 5  | The        | Heuristic Algorithm                                                 | 201        |

|     | 6  |            | ulated Annealing                                                    | 205        |

|     |    | 6.1        | The Simulated Annealing Algorithm                                   | 205        |

|     |    | 6.2        | Initial Solution and Parameter Selection                            | 206        |

|     |    | 6.3        | Neighbouring Solution in Test Scheduling                            | 206        |

|     |    | 6.4<br>6.5 | Neighbouring Solution in Scheduling and TAM Design<br>Cost function | 206<br>207 |

|     | -  |            |                                                                     |            |

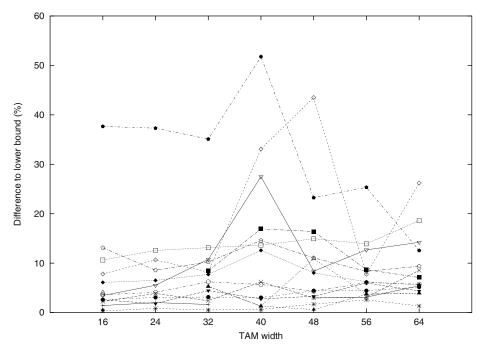

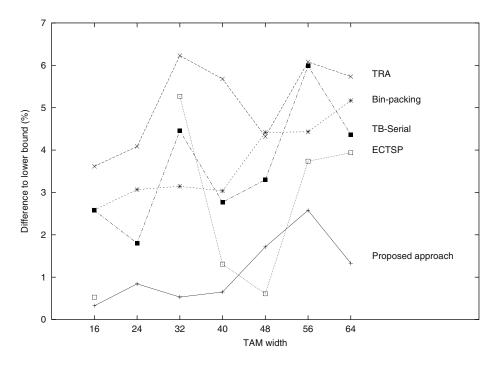

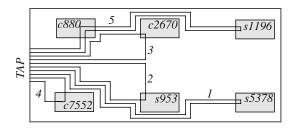

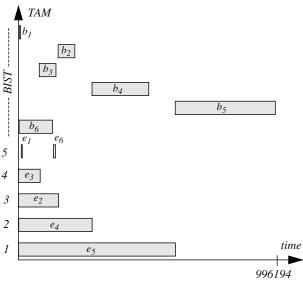

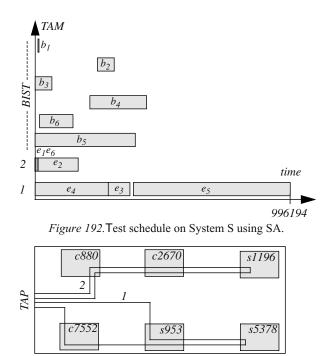

|     | 7  | -          | erimental Results                                                   | 208        |

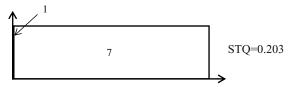

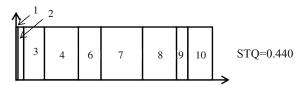

|     |    |            | Benchmarks<br>Test Scheduling                                       | 208<br>208 |

|     |    |            | Test Resource Placement                                             | 208        |

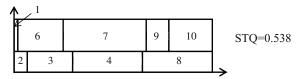

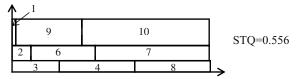

|     |    | 7.4        |                                                                     | 209        |

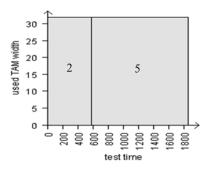

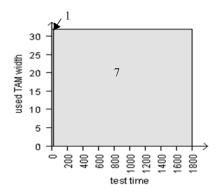

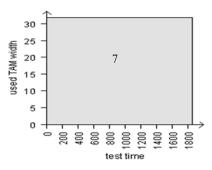

|     |    | 7.5        | Test Scheduling and TAM Design                                      | 211        |

|     | 8  |            | clusions                                                            | 214        |

|     |    |            |                                                                     |            |

| 12. | EF |            | ENT TEST SOLUTIONS FOR CORE-BASED DESIGNS                           | 215        |

|     | 1  |            | oduction                                                            | 215        |

|     |    | 1.1        | Introduction                                                        | 215        |

|     | 2  | Bacl       | kground and Related Work                                            | 217        |

|     | 3  |            | Problems                                                            | 221        |

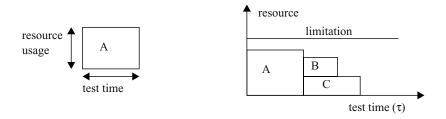

|     |    | 3.1        | Test Time                                                           | 221        |

|     |    | 3.2        | Test Power Consumption                                              | 226        |

|     |    | 3.3        | Test Power Consumption at Test Parallelization                      | 229        |

|     |    | 3.4        | Test Resource Limitations                                           | 230        |

|     |    | 3.5        | Test Conflicts                                                      | 231<br>232 |

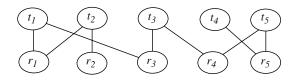

|     |    | 3.6<br>3.7 | Test Access Mechanism Design<br>System Modeling                     | 232<br>233 |

|     |    | 5.1        | System wouldning                                                    | 233        |

|     | 4  | Our Approach                                             | 237 |

|-----|----|----------------------------------------------------------|-----|

|     |    | 4.1 Bandwidth Assignment                                 | 238 |

|     |    | 4.2 Test Scheduling                                      | 239 |

|     |    | 4.3 TAM Planning                                         | 240 |

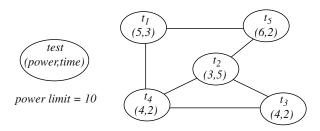

|     |    | 4.4 An Example                                           | 242 |

|     |    | 4.5 TAM Optimization                                     | 244 |

|     |    | 4.6 Complexity                                           | 246 |

|     | 5  | Experimental Results                                     | 246 |

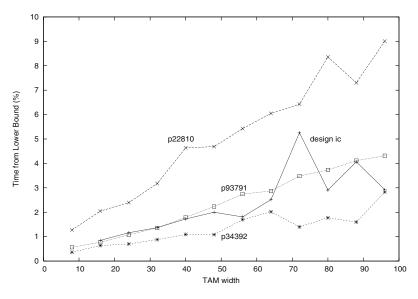

|     |    | 5.1 Test Scheduling                                      | 246 |

|     |    | 5.2 Integrated Test Scheduling and TAM Design            | 247 |

|     |    | 5.3 Test Scheduling, Test Parallelization and TAM Design | 249 |

|     | 6  | Conclusions                                              | 250 |

| 13. | CC | DRE SELECTION IN THE SOC TEST DESIGN-FLOW                | 253 |

|     | 1  | Introduction                                             | 253 |

|     | 2  | BACKGROUND                                               | 254 |

|     | 3  | Related Work                                             | 257 |

|     | 4  | Problem Formulation                                      | 260 |

|     |    | 4.1 Problem Complexity                                   | 263 |

|     | 5  | Test Problems and Their Modeling                         | 263 |

|     |    | 5.1 Test Time                                            | 263 |

|     |    | 5.2 Test Power Consumption                               | 264 |

|     |    | 5.3 Test Conflicts                                       | 267 |

|     | 6  | Test Design Algorithm                                    | 268 |

|     |    | 6.1 Resource Utilization                                 | 271 |

|     |    | 6.2 Example                                              | 271 |

|     | 7  | Experimental Results                                     | 273 |

|     | 8  | Conclusions                                              | 275 |

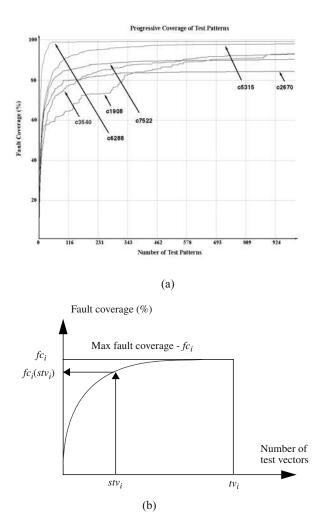

| 14. | DF | EFECT-AWARE TEST SCHEDULING                              | 277 |

|     | 1  | Introduction                                             | 277 |

|     | 2  | Related Work                                             | 278 |

|     | 3  | Sequential Test Scheduling                               | 279 |

|     | 4  | Concurrent Test Scheduling                               | 280 |

|     |    | 4.1 Test Sets with Fixed Test Times                      | 281 |

|     |    | 4.2 Test Sets with Flexible Test Times                   | 282 |

|     |    | 4.3 Test Scheduling Algorithms                           | 283 |

|     | 5  | Experimental Results                                     | 286 |

|       | 6                                                                                               | Conclusions                               | 286 |  |  |

|-------|-------------------------------------------------------------------------------------------------|-------------------------------------------|-----|--|--|

| 15.   | AN INTEGRATED TECHNIQUE FOR TEST VECTOR SELECTION<br>AND TEST SCHEDULING UNDER ATE MEMORY DEPTH |                                           |     |  |  |

|       |                                                                                                 | NSTRAINT                                  | 291 |  |  |

|       | 1                                                                                               | Introduction                              | 291 |  |  |

|       | 2                                                                                               | Related Work                              | 293 |  |  |

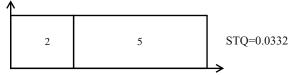

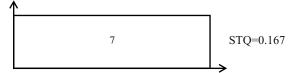

|       | 3                                                                                               | Problem Formulation                       | 295 |  |  |

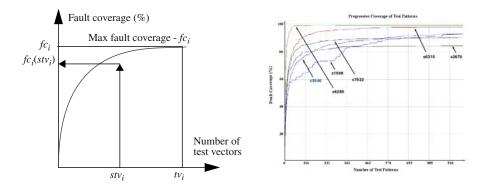

|       | 4                                                                                               | Test Quality Metric                       | 296 |  |  |

|       | 5                                                                                               | Test Scheduling and Test Vector Selection | 299 |  |  |

|       |                                                                                                 | 5.1 Illustrative Example                  | 301 |  |  |

|       | ~                                                                                               | 5.2 Optimal Solution For Single TAM       | 305 |  |  |

|       | 6                                                                                               | Experimental Results                      | 305 |  |  |

|       | 7                                                                                               | Conclusions                               | 307 |  |  |

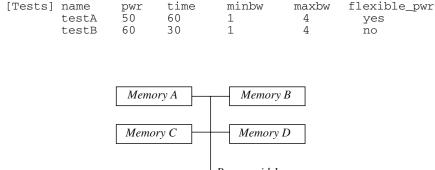

| App   | endi                                                                                            | x 1. Benchmarks                           | 321 |  |  |

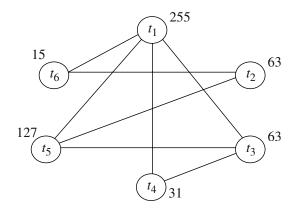

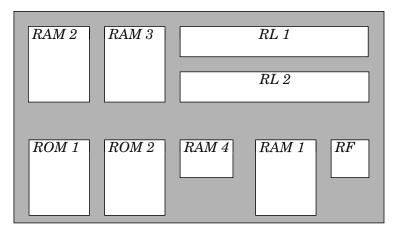

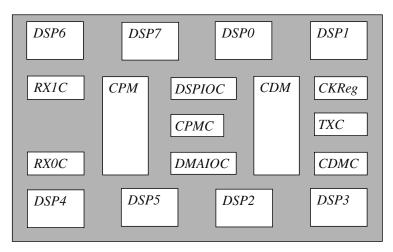

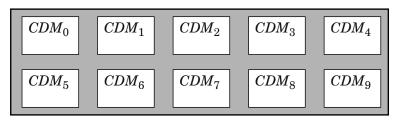

|       | 1                                                                                               | Introduction                              | 321 |  |  |

|       | 2                                                                                               | Format of the inputfile                   | 321 |  |  |

|       | 3                                                                                               | Design Kime                               | 324 |  |  |

|       | 4                                                                                               | Design Muresan 10                         | 326 |  |  |

|       | 5                                                                                               | Design Muresan 20                         | 327 |  |  |

|       | 6                                                                                               | ASIC Z                                    | 329 |  |  |

|       | 7                                                                                               | Extended ASIC Z                           | 331 |  |  |

|       | 8                                                                                               | System L                                  | 333 |  |  |

|       | 9                                                                                               | Ericsson design                           | 335 |  |  |

|       | 10                                                                                              | System S                                  | 349 |  |  |

| Refe  | renc                                                                                            | es                                        | 353 |  |  |

| Index |                                                                                                 |                                           |     |  |  |

# Preface

Advances in both semiconductor processing technologies as well as integrated circuit (IC) design techniques and tools have enabled the creation of micro-electronic products that contain a huge amount of complex functionality on a single die. This allows the integration into a single IC of the components that traditionally resided on one or multiple printed circuit boards. As the latter traditional product was commonly referred to as "system", a modern IC that contains the same functionality goes by the name "System-On-Chip" or SOC. The benefits of this ongoing integration are obvious: (1) a smaller form factor, as we want small products that fit our pockets, (2) higher performance, as our needs to do, hear, see more with micro-electronics seem insatiable, and (3) lower power, as these portable, mobile products work of batteries with a limited energy budget.

Designing SOCs is a challenge. The functional and layout designs need to be modular and hierarchical, as flat design is no longer an option for such "monster chips". Increasingly, also the on-chip interconnect becomes hierarchical; we refer to this as Network-On-Chip or NOC. In order to reduce timeto-market and leverage external expertise, we see large modules being imported and reused. The latter design practice has divided the IC design community into 'core providers' and 'SOC integrators'.

Testing SOCs brings forward new challenges as well. The only viable way to contain the growing complexity of SOCs is to apply a modular test approach. Modular testing is required (1) for heterogeneous SOCs, which contain non-logic modules, such as embedded memories, analog and RF modules, e-FPGAs, etc., and (2) for black-boxed third-party cores, for which the test is developed by the core provider, but applied by the SOC integrator. However, modular testing also has precious benefits in terms of (3) reduced test pattern generation efforts due to "divide-n-conquer", and (4) test reuse over multiple generations of SOCs. The research challenges related to a modular test approach are the following.

- Design and test development is distributed over multiple parties, companies, geographical locations, and time. This brings with it challenges with respect to the transfer of "test knowledge" from core provider to SOC integrator.

- Cores and other modules are typically deeply embedded within the SOC, without direct access to SOC pins or other test resources. Hence, we need to add an on-chip test access infrastructure, that enables proper testing of the SOC, but that is as much as possible transparent when not in test mode.

- The fact that there is no longer one monolithic chip test, but many smaller tests instead, brings with it many optimisation issues with respect to test coverage, test application time, power dissipation during test, silicon area used by the on-chip infrastructure, etc. Designers and test engineers need support to make the right choices in this complex matter, where everything seems to be related with everything.

This book by my fellow researcher Erik Larsson tries to shed light on the many issues that come to play in the arena of modular SOC testing. It was written from the need to have a book that could serve as text book for university students. On the one hand, several text books are available on the fundamentals of classical test approaches. On the other hand, available books on modular SOC testing have too much a research nature and too little of introductory material to serve the purpose of student text book. And indeed, Larsson's book exactly fits the void in between these two categories.

This book consists of three parts. In Part 1, the book starts out with a brief overview of classical test approaches. This provides the type of introduction someone new in the field will need, with many references to the well-known text books for further, in-depth coverage. Part 2 describes the challenges and problems specific to testing large, modular, and heterogeneous SOCs. The experienced reader is suggested to right away jump to this part of the book. Subsequently, Part 3 provides details of the research work Larsson and his team have done to address these research challenges. The central key word in all these solutions is "integration"; integration of design and test, and integration of solutions to tackle the many multi-faced optimisation problems at hand. The entire book is written in the very clear style that also marks Larsson's research papers and presentations. I strongly believe that a modular and hence scalable approach is the only feasible way forward to address the manufacturing test challenges of ICs that are every-increasing in size and complexity. Hence, I do recommend this book; to researchers, to test methodology developers at EDA companies, to design and test engineers, and of course to university students.

ERIK JAN MARINISSEN Principal Scientist Philips Research Laboratories Eindhoven, The Netherlands

# Acknowledgements

This book would not have been written without the help of many. I would like to thank Zebo Peng, Petru Eles, and the rest of the group at Embedded Systems Laboratory at the Department of Computer and Information Science at Linköpings Universitet, Sweden. I would like to thank Julien Pouget, Stina Edbom, Klas Arvidsson, and Per Beijer for their contributions to the book. And I would like to thank Krishendu Chakrabarty, Erik Jan Marinissen, and Vishwani D. Agrawal for comments on the draft. I would like to thank Hideo Fujiwara for the time in Japan, Mark de Jongh for inspiration and Cindy Zitter for encouragements, and finally friends and familly.

> ERIK LARSSON Linköpings Universitet Linköping, Sweden

# PART 1 TESTING CONCEPTS

# Chapter 1

# Introduction

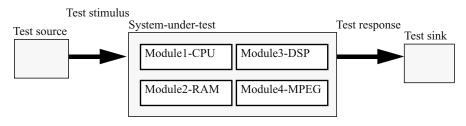

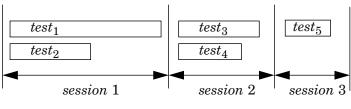

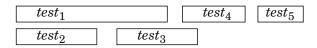

The aim of this book is to discuss production test, including related problems, their modeling, and the design and optimization of System-on-Chip (SOC) test solutions. The emphasis is on test scheduling, how to organize the testing, which is becoming important since the amount of test data is increasing due to more complex systems to test, and the presence of new fault types because of device size miniaturization. The focus of the discussion in the book is on the system perspective since the increasing complexity of SOC designs makes it harder for test designers to grasp the impact of each design decisions on the system's test solution, and also because locally optimized test solution for each testable unit do rarely lead to globally optimized solutions.

An important aspect when taking the system perspective is the computational cost versus modeling and optimization granularity. A fine grain model taking a high number of details into account is obviously to be preferred compared to a model that is considering only a few details. However, a fine grain model leads to high computational cost, and the computational cost is important to keep under control since the SOC designs are increasing in size, and also since the nature of the design process of test solutions is an iterative process. Furthermore, as the number of design parameters increases, which makes the design space large, it is of most import to decide on which problems to spend the computational effort.

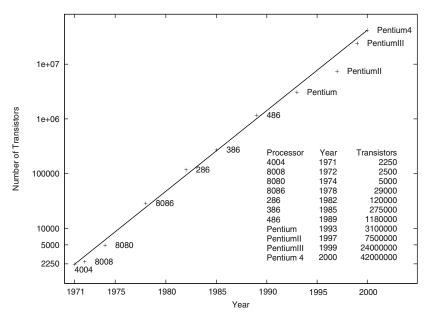

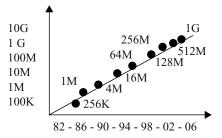

The number of transistors per chip has increased enormously over the years. Moore predicted that the number of transistors per chip should roughly double every eighteen months [198]. In Figure 1, the prediction (Moore's law) versus the actual number of transistor per processor is plotted for some Intel processors. The prediction has been amazingly precise.

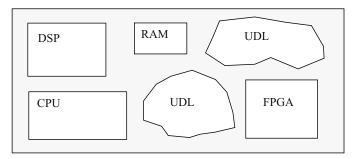

Chip design is a challenge driven by the increasing number of transistors, device size miniaturization, and shorter development times. An increasing number of transistors can be handled by modeling the system at higher abstraction levels; however, device size miniaturization requires early knowledge of the design at transistor-level. The design times can be shortened by reusing previous designs, or parts (modules or cores) of previous designs. A core-based design methodology is an alternative since it allows pre-defined and pre-verified blocks of logic, so called cores, to be combined with glue logic to become the designed system. The cores can be reused from previous designs or bought from core vendors.

The SOC integrator is the person that designs the system. The design work includes decision on which cores to be used in the design and how the cores

*Figure 1*. The number of transistors for some Intel processors (points) and the Moore's law prediction (straight line) [107, 198].

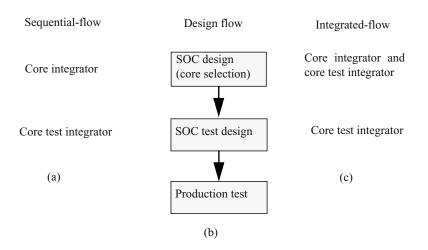

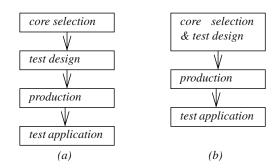

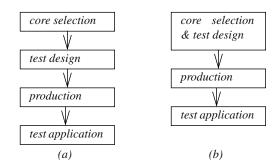

should be combined to a system. Each of the cores in the design may origin from previous designs within the company, or can be bought from some other companies (core vendors), or can be completely newly designed. The SOC test integrator is the person that designs the test solution for the system. Figure 2(b) shows a simplified SOC design flow. In Figure 2(a) the work by the SOC integrator and the SOC test integrator is organized in a sequence. The SOC test integrator starts working on the test solution when the SOC integrator has fixed and finished the design. An alternative to a sequential design flow is shown in Figure 2(c) where the SOC test integrator takes part as early as in the SOC design. The advantage of the latter approach is that the SOC test integrator can have an impact on design decisions; the selections of cores. In such a design flow, it becomes obvious that the SOC test integrator needs support, *i.e.* tools, for the evaluation of different design decisions. For instance, if two different processor cores can solve the same problem, but the two processors have different test characteristics, which one should the SOC test integrator select?

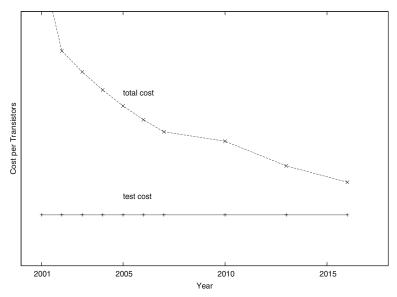

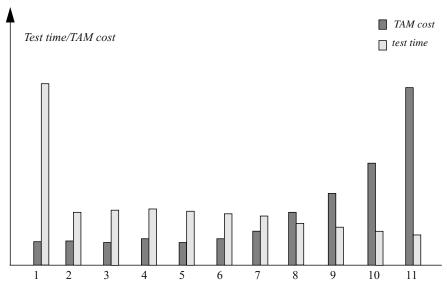

A motivation for considering the test cost as early as in the design phase is that the test cost is becoming a bottleneck. In Figure 3, the expected cost-pertransistor and the expected test-cost-per-transistor are plotted [106]. The number of transistor per chip increases, but interestingly, the cost-per-transistor is

*Figure 2*. The system-on-chip design flow, the involved persons in (a) a sequential design flow and (b) in an integrated design flow.

decreasing. Interesting is also that the test-cost-per-transistor keeps constant, however, the trend is clear from Figure 3; the relative test cost per designed transistor is increasing.

Among expected challenges are that device size miniaturization and increasing performance lead to new fault types that require new fault models. New models will further increase the amount of test data for an SOC design, and hence the testing times are becoming longer, making test scheduling even more important. Moore [198] pointed out that the transistor count will increase drastically, but also that the power consumption-per-transistor will decrease. It is likely that there will be a time when the transistors can be designed, but the power to make them work will enforce limitations. For designers who want to implement an increasing functionality in the system this might be frustrating. However, the test design community can take advantage of this fact. It means that the cost of additional DFT logic is reduced. Logic can be introduced as logic only used for test purpose. And, logic redundancy can also be used, for instance, to improve yield. The power dissipation during testing is another important problem. In order to detect as many faults as possible per test vector, it is desirable to activate as many fault locations as possible. High activity in the system leads to higher power consumption. The system's power budget can be exceeded, the allowed power consumption for each power grid can be exceeded, and also a testable unit can during testing consume such amount of power that the system is damaged.

*Figure 3*. The predicted cost per transistor versus the predicted test cost per transistor [106].

This book is dived into three parts. Part one contains the following chapters, an introduction of the topic (Chapter 1), the design flow (Chapter 2) and the test problems (Chapter 3), system modeling (Chapter 5), test conflicts (Chapter 6), and test power consumption (Chapter 7). Part two contains the two chapters; Chapter 8 were TAM design approaches are described and Chapter 9 where test scheduling is discussed. The third part discusses applications in detail. The part is a compilation of a set of papers covering test scheduling using reconfigurable core wrappers, test scheduling and TAM design, core selection integrated in the test solution design flow, and defectoriented test scheduling.

# Chapter 2

# **Design Flow**

## **1 INTRODUCTION**

The aim with this chapter is to give a brief introduction to design flow in order to motivate the discussion on modeling granularity in the following chapters.

The pace in the technology development leads to an extreme increase of the number of transistor in a system (See *Introduction* on page 1). However, there is a gap between what is possible to design according to what the technology development allows to be designed and what is possible to design in terms of cost (time, money, manpower). The so called productivity gap, which is increaseing, is the difference between what is possible to design using available technologies and what is reasonable to accomplish in reasonable design time. The productivity is defined as [120]:

$$P = \frac{\text{total gate count}}{\text{development time } \times \text{number of designers}}$$

It means that if productivity keeps stable, the design time would increase drastically (keeping the design team size constant). An alternative is to increase the size of the design teams in order to keep design time constant. Neither of the approaches are viable. Instead, the evolution in EDA (Electronic Design Automation) will provide productivity improvements. That means that better modeling and optimization techniques have to be developed.

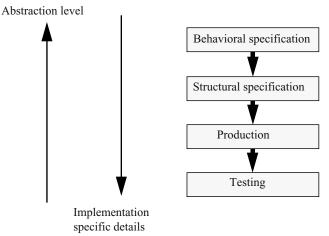

In order for the designers to handle the complexity of the designs due to the technology development, the system can initially be modeled at a high abstraction level. Semi-automatic synthesis and optimization steps (Computer-Aided Design (CAD) tools guided by designers) on the high-level specification transforms the design from the abstract specification to the final circuit ( see Figure 4). System modeling at an high abstraction level, means that less implementation specific details are included compared to a system model at lower abstraction levels. Gajski *et al.* [64] view the design flow using a Y-chart where the three direction behavior, structure, and geometry.

Figure 4. Design flow.

### 2 HIGH-LEVEL DESIGN

The advantage of a top-down design flow, specifying the design a high abstraction level with less implementation specific details, and through synthesis move to a model with a high degree of implementation specific details, is that design exploration, where design alternatives easily can be explored, is eased. A model at high abstraction level includes fewer details and therefore the handling of the design becomes easier, and more optimization steps can be allowed, which means a more thorough search in the design space.

In the design flow, the system is modeled. The purpose of modeling is to understand the function of the system as well as adding implementation specific details. A number of techniques have been developed. On initiative by VHSIC (Very High Speed Integrated Circuits) programme the description language for digital circuits called VHDL (VHSIC Hardware Description Language) was developed [120]. VHDL became an IEEE standard in 1987, and the latest extension took place in 1993 [268]. Graphical descriptions are useful for humans to more easily understand the design. Examples of graphical descriptions are Block Diagrams, Truth Tables, Flow Charts, State Diagrams (Mealy and Moore state machine), and State Transition Diagrams. Netlists are used to enumerate all devices and their connections. The SPICE (Simulation Program with Integrated Circuit Emphasis) is an example of a device oriented structure [265]. The EDIF (Electronic Design Interchange Format) was developed to ease transport of designs between different CAD systems. And, for capturing delay formats in the design, the SDF (Standard Delay Format) was developed [252].

#### **3 CORE-BASED DESIGN**

There are a number of disadvantages with a top-down design flow. One obvious is that at high abstraction level implementation details are less visible. It makes discussion on certain detailed design aspects impossible at high abstraction level. The problem with high abstraction levels where less information is captured has become a problem in sub-micron technology where technology development has lead to high device size miniaturization that requires knowledge of transistor-level details. Another fundamental problem is that in a top-down design flow, there is a basic assumption that the system is designed for the first time. In reality, very few systems are designed from scratch. In most cases, there exists a previous system that is to be updated. It means that small parts or even large part of the previous system can be reused for the new system. Also, other previously designed blocks that have been used in a completely different system can be included in the new system. It can also be so that blocks of logic, cores, are bought from other companies. For instance, CPU cores can be bought from different companies and used in the design.

In the core-based design environment, blocks of logic, so called cores, are integrated to a system [84]. The cores may origin from a previous design developed at the company, it may be bought from another company, or it can be a newly designed core. The *core integrator* is the person that selects which cores to use in a design, and the *core test integrator* is the person that makes a design testable - designs the *test solution*. The core integrator selects core from different *core providers*. A core provider can be a company, a designer involved in a previous design, or a designer developing a new core for the system.

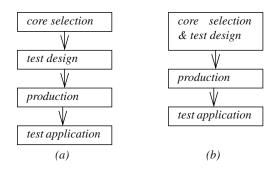

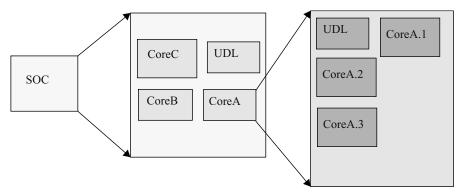

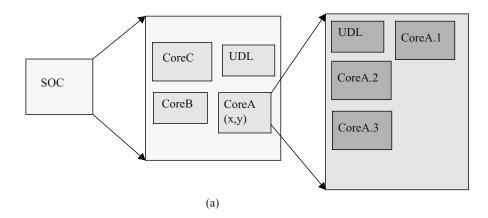

A core-based design flow is typically a sequence that starts with core selection, followed by test solution design, and after production, the system is tested (Figure 5(a)). In the core selection stage, the core integrator selects appropriate cores to implement the intended functionality of the system. For each function there are a number of possible cores that can be selected, where each candidate core has its specification on, for instance, performance, power consumption, area, and test characteristics. The core integrator explores the design space (search and combines cores) in order to optimize the SOC. Once the system is fixed (cores are selected) the core test integrator designs the TAM and schedules the tests based on the test specification for each core. In such a design flow (illustrated in Figure 5(a)), the test solution design is a consecutive step to core selection. In such a flow, even if each core's test solution is most likely not highly optimized.

Figure 5.Design flow in a core-based design environment (a) traditional and (b) proposed.

The design flow in Figure 5(b), on the other hand, integrates the core selection step with the test solution design step, making it possible to consider the impact of core selection when designing the test solution. In such a design flow (Figure 1(b)), the global system impact on core selection is considered, and the advantage is that it is possible to develop a more optimized test solution.

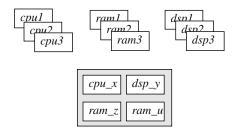

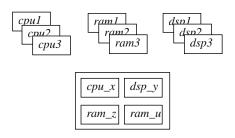

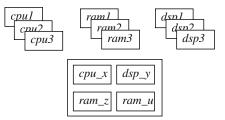

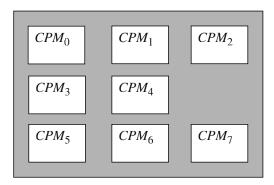

The design flow in Figure 1(b) can be viewed as in Figure 6, where the core type is floor-planned in the system but there is not yet a design decision on which core to select. For each position, several cores are possible. For instance, for the cpu\_x core there are in Figure 6 three alternative processor cores (cpu1, cpu2 and cpu3).

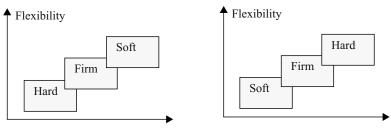

In general, the cores can be classified as:

- soft cores,

- firm cores, or

- hard cores.

A soft core is given as a specification that has to be synthesized, while a hard core is already a fixed netlist. A firm core is somewhere between a soft core and a hard core. A soft core is therefore the most flexible type of core;

Figure 6.System design.

however, it requires the tools, effort and time involved in the work of synthesizing it to a gate-level netlist. A hard core, on the other hand, is already fixed and ready to be used in the design. Hence, less effort and time are required for the optimization of the core. The difference between a soft core, firm core, and a hard core is also visible when it comes to testing. For soft core there is a higher degree of freedom when determine the test method compared to hard cores where the test method and test vectors are more fixed.

## 3.1 Network-on-Chip

A problem when the SOC designs grow in complexity is that the on-chip interconnections, such as buses and switches, can not be used anymore due to their limited scalability. The wires are simply becoming too long. An alternative is to use networks on chip (NOC) [14, 121].

## 3.2 Platform-Based Design

The design flow must not only take the development of the hardware into account but also the development of software. Systems of today include an increasing number of programmable devices. The software (operating system and application programs as well as compilers) must be developed. In order to fix the architecture, the concept of platform-based design has been developed. Sangiovanni-Vincentelli [237] compare it with the PC (personal computer):

- The X86 instruction set makes it possible to re-use operating systems and software applications,

- Busses (ISA, USB, PCI) are specified,

- ISA interrupt controller handles basic interaction between software and hardware,

- I/O devices, such as keyboard, mouse, audio and video, have a clear specification.

The PC platform has eased the development for computers. However, most computers are not PCs but embedded systems in mobile phones, cars, etc [266]. Hence, a single platform-based architecture for all computer systems is not likely to be found.

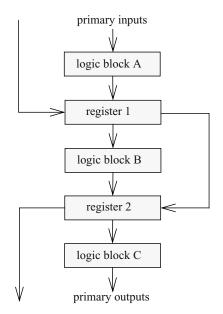

# 4 CLOCKING

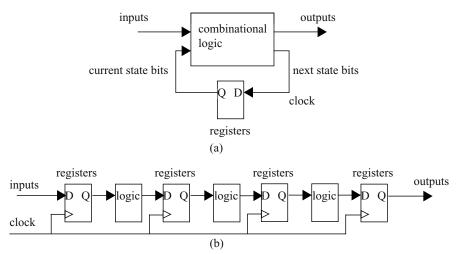

Clocking the system is becoming a challenge. Higher clock frequencies are making timing issues more important. The storage elements (flip-flops forming registers) in a system have to be controlled. For instance, Figure 7(a) shows a finite state machine (FSM), and a pipelined system is in Figure 7(b); the storage devices are controlled by the clock. Most systems are a combination of FSM and pipelined systems.

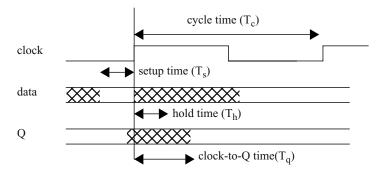

The input of a register (flip-flop) is commonly named D, and the output named Q. Figure 8 illustrates the following:

- the setup time  $(T_s)$  the time required before the edge until the value is stable at the *D* input,

- the *hold time*  $(T_h)$  the time required after the edge in order store the value in the register,

- the *clock-to-Q delay*  $(T_q)$  the time required after the edge in order to produce the value on Q,

- the cycle time  $(T_c)$  the time between two positive edges (from 0 to 1).

The registers can be design for instance as a *level-sensitive latch*, *edge-trigged register*, *RS latch*, *T register*, and *JK register* [277].

Figure 7. Clocked systems. (a) a finite state machine (FSM); (b) a pipelined system.

Figure 8. Single phase clocking and its parameters.

## 4.1 System Timing

Latches and registers can be used in different ways to implement a clocked system [277]. It is important that the clock signal is delivered to the registers correctly. Long wires may introduce delays in the clock distribution leading to clock skew - the clock signal is not delivered at the same time to all clocked elements.

The cycle time  $(T_c)$  is given by:

$$T_c = T_q + T_d + T_s$$

where  $T_q$  is the clock-to-Q delay,  $T_s$  is the setup time, and  $T_d$  is the worstcase delay through the combinational logic blocks.

### 4.2 Clock Distribution

Clock distribution is a problem. For instance, the total capacitance in the system that has to be driven can be above 1000 pF [277]. Driving such capacitance at high repetition rate (clock speed) creates high current (see example in Figure 9).

```

\begin{array}{l} V_{DD} = 5V \\ C_{reg} = 2000 \ pF \ (20K \ register \ bits \ @ .1pF \\ T_{clk} = 10 \ ns \\ T_{rise/fall} = 1 \ ns \\ \\ I_{peak} = Cx \\ Pd = CXV_{dd}^2 \times f = 2000 \times 10^{-12} \times 5100 \times 10^{-6} \end{array}

```

Figure 9. Example illustrating high current and power [277].

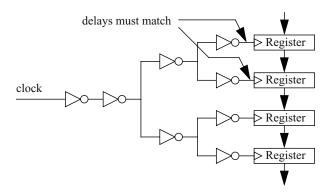

Figure 10.Distributed clock-tree where the logic is omitted.

The clock can be distributed using [277]:

- a single large buffer (*i.e.* cascaded inverters) that is used to drive all modules, or

- a distributed-clock-tree approach (Figure 10).

# 4.3 Multiple Clock Domains

In a core-based design, a set of cores are integrated to a system. Each core might require its dedicated clock speed. A design with multiple clock domains can present challenges. A typical problem is at the clock-domain boarders where one clock frequency is meeting another clock domain. Problems that can appear are, for instance, data loss and metastability. Data loss can appear when data generated by clock1 is not captured by clock2 until it has already been changed. Such problems appear if the destination clock is running at a higher speed. Metastability is due to that there is no timing relation between source and destination clock domain, and it can happen that data and clock signals reach the flip-flops at the same time. Metastability can cause reliability problems.

## 4.3.1 Phase Locked Loop (PLL)

A phase locked loop (PLL) is used to generate internal clocks in the system for two main reasons [277]:

- Synchronize the internal clock with an external clock.

- The internal clock should operate at a higher frequency than the external clock.

The increasing on-chip clock speed has lead to clock skew problems. A PLL allows an internal clock to be generated that is in phase with an external clock.

## 4.3.2 Globally-Asynchronous Locally-Synchronous

The advantage of making a system synchronous is that it is:

- a proven technique, and

- wide-spread EDA tools are available.

However, it is important to note that

- clock speed limited by slowest operation,

- clock distribution a problem,

- hard to design systems with multiple clock domains, and

- energy is consumed for idle operation.

An alternative is to make the system asynchronous. Instead of synchronize based on a clock, the system is controlled through communication protocol (often hand-shaking). The advantages with such a system are that is:

- "average-case" performance,

- no clock signal to distribute, and

- no energy for idle operations.

The disadvantages with the asynchronous design approach are that:

- limited EDA supports, and

- extremely difficult to test.

Chapiro [36] proposed a scheme named Globally-asynchronous locallysynchronous (GALS) where there is an asynchronous wrapper around each core/block and where each core itself is synchronous. FIFO queues are inserted at the boundaries between the asynchronous and the synchronous parts.

The advantages with GALS are:

- easy to design systems with multiple clock domains,

- no global clock to distribute,

- power efficient system only operates when data is available,

- asynchronous circuits (and related problems) limited to the wrapper, and

- main functional blocks designed using conventional EDA tools.

Among the disadvantages is the area overhead for self-timed wrapper. Implementations has shown about 20% power saving at 10% area increase.

## 5 **OPTIMIZATION**

Optimization problems can be mapped to well-known problem. The advantage by doing that is that if it is known that the well-known problem is NP-complete, the mapped problem is also NP-complete. The *Knap-sack problem* and the *fractional Knap-sack problem* are interesting for scheduling problems. The Knap-sack problem where given items of different values and volumes, the problem is to find the most valuable set of items that fit in a knapsack of fixed volume. The decision problem, if an item should be included in the knap-sack or not, is NP-hard [42]. However, the *fractional Knap-sack problem* where given materials of different values per unit volume and maximum amounts, find the most valuable mix of materials which fit in a knapsack of fixed volume. Since we may take pieces (fractions) of materials, a greedy algorithm finds the optimum. Take as much as possible of the material that is most valuable per unit volume. If there is still room, take as much as possible of the next most valuable material. Continue until the knapsack is full and the result is an optimal solution [42].

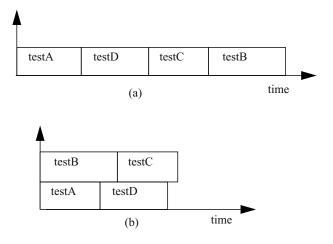

The test scheduling problem for systems where all tests are given and all are assigned a fixed testing time and the objective is to minimize the test application time is in the case when sequential testing is assumed trivial. The optimal test application time  $\tau_{application}$  is for a system with *N* tests each with a test time  $\tau_i$  (*i*={1..*N*} given by:

$$\tau_{\text{application}} = \sum_{i=1}^{N} \tau_i \tag{2.1}$$

The assumptions that only one test at a time can be active at any moment, and that all tests have to be applied, means that any order of the tests is optimal. An algorithm iterating in a loop over all tests is required and at each iteration one test is selected and given a start time. The computational complexity of such an algorithm depends linearly on the number of tests, O(n) - n is the number of tests, hence the algorithm is polynomial (*P*). Most problems cannot be solved, that is an optimal solution is found, in polynomial time. The

| task A resource_1 resource_2 | resource_1 | task_A task_B |

|------------------------------|------------|---------------|

| task B                       | resource_2 | task_B        |

| task C resource_3            | resource_3 | task_C        |

#### Figure 11.Gantt chart.

problems are then said to be *NP-complete* (non-deterministic polynomial time). Until today, there is no algorithm that in polynomial time guarantees to find the optimal solution for NP-complete problems. At present, all known algorithms for NP-complete problems require time which is exponential in the problem size [42]. Therefore, in order to solve an NP-complete problem for any non-trivial problem size, a heuristic can be used.

*Optimization* is the search for a solution that minimizes a given cost function where the ultimate goal is to find the *optimal solution* (no better solution can be found). An algorithm that guarantees to find the global optimum is an exact algorithm. In many cases, the problems are NP hard and a heuristic algorithm finds a solution that locally, not globally, optimizes the cost function. A heuristic *can* find the optimal solution, however, there is *no guarantee* that the optimal solution is found. A heuristic is often a trade-off between computational cost (CPU time) and computational quality (how far is the solution from the optimal solution).

In practice, the obvious problem with a heuristic is to evaluate the quality, that is how close is the solution produced from the heuristic compared to the optimal solution (the optimal solution is only guaranteed with exhaustive search, which is not possible due to time constraint). A lower bound can help a designer for instance in giving a feeling on how close to a lower bound a certain solution is. Often a resource limits a solution, and knowledge about the resources can guide the evaluation of the quality of a solution. A way to model resource utilization is to use a Gantt chart [23]. A Gantt chart can either be job (task)-oriented or resource oriented (figure 11). In figure 11(b) task\_A and task\_B both use resource \_1 and it is obvious that resource\_1 is used most, and hence, will most likely be the reasons for a bottleneck. A Gantt-chart can be used to define a lower bound on the test application time of a system, for instance. A lower bound is the lowest possible cost of a solution. Note that defining a way to compute a lower bound does not mean it is a way to find a solution corresponding to that the lower bound is found.

Above it was shown that it is trivial to develop an optimal test schedule in respect to test time for a sequential architecture when all tests are given a fixed test time and the objective is to minimize the test application time. In sequential testing, only one test at a time can be active, and that means that no constraint can limit the solution. In concurrent test scheduling, where more than one test can be applied at a time, conflicts often limits the solution. The problem to minimize the test application time using concurrent test scheduling for a system where all tests are given a fixed testing time *under no constraint* is trivial. All tests are simply started at time point zero. The optimal test application time  $\tau_{application}$  is for a system with *N* tests each with a test time  $\tau_i$  (*i*={1..*N*} given by:

$$\tau_{\text{application}} = \max\{\tau_i\}$$

(2.2)

The concurrent test scheduling problem, more than one test can be executed at the same time, is in general not *NP*-complete. However, the concurrent test scheduling problem *under constraint* is *NP*-complete. We will discuss this in more detail below.

#### 5.1 **Optimization Techniques**

The search for a solution can be done using exhaustive search or using some heuristics. The advantage of exhaustive methods is that an optimal solution is found. The problem is that most problems are complicated (NP-hard), which means that the computational effort (CPU time) is unacceptable for larger instances of the problem.

The most straight forward optimization approach is exhaustive search. It means that every single solution in the search space is evaluated and the best solution is reported. Below are a selection of such approaches, namely: *backtracking*, *branch-and-bound*, *integer-linear programming*. Iterative algorithms that iteratively search for an optimized solution but cannot guarantee that optimal solution is found are heuristics such as for instance: *local search*, *simulated annealing*, *genetic algorithms* and *tabu search*. These heuristics are iterative, that is from an initial solution an optimized solution is created through iterative modifications (transformations). A heuristic can be constructive - the solution is constructed from scratch. A constructive heuristic is used in an iterative transformation-based heuristic. The computational cost of an constructive algorithm is often in the range of  $N^x$  where x=2, 3, 4.

#### 5.1.1 Backtracking and Branch-and-bound

The idea when using backtracking for an exhaustive search is to start with an initial solution where as many variables as possible are left unspecified [67]. The back-tracking process assigns values to the unspecified values in a systematic way. As soon as all variables are assigned to valid values, the cost of the feasible solution is computed. Then, the algorithm back-track to a partial solution assigning next value to the unspecified variables. Often it is not needed to visit all solutions that are produced in the backtracking process. Therefore the solution space is in back-tracking evaluated in a search tree. The idea in branch-and-bound is to not traverse sub-trees where the cost is higher than the best cost so far. If the cost of the solution of a partial specified solution is worse than the best solution, the sub-tree can be killed or pruned, which means that the sub-tree is not traversed. The search for a solution can be done in a depth-first or breath-first manner.

#### 5.1.2 Integer Linear Programming

Integer Linear Programming (ILP) is a way to transform combinatorial optimization problems into a mathematical format. A high number of problems can relatively easily be reduced to ILP [67]. However, from a computational point of view, this does not help since ILP is NP-complete itself. Nevertheless, there exists a number of general ILP-solvers, which means that if the optimization problem can be modeled as an ILP instance, the software (program) solves the problem. The main advantage of using an ILP-solver is that an exact solution is found. The draw-back is, obviously, the computational cost for larger problems.

ILP is a variant of Linear programming (LP). LP problems can be solved the polynomial-time *ellipsoid algorithm*, however, it is in practice outperformed by the *simplex algorithm* which has a worst-case time complexity [67]. ILP is a variant of LP where variables can only be integers [67].

#### 5.1.3 Local Search

Local search is an iterative method that search a *local neighborhood* instead of searching the whole search space when creating the new solution [67]. The idea is to search the neighborhood and by using modifications called move or local transform the current solution is improved. The best solution, found using exhaustive search in the local neighborhood (*steepest decent*), is used as the next solution. In practice the search in the local neighborhood can be terminated at *first improvement*. The first improvement makes use of less computational cost compared to the steepest decent. However, in steepest decent each iteration creates a better solution, which can lead to less required iterations, hence less computational cost, compared to using first improvement. In order to avoid getting stuck at local optimum, a larger neighborhood can be used. However, if a larger neighborhood is to be considered, higher computational cost is required to search the neighborhood. Local search does not allow moves out of local optimum, so called uphill moves, as allowed in Simulated Annealing and Tabu Search.

#### 5.1.4 Simulated Annealing

Simulated Annealing (or statistical cooling) proposed by Kirkpatrick *et al.* [131] is an optimization technique that is analogous to a physical process [67]. Initially, the material is heated up so that the molecules can move freely (the material is liquid). The temperature is slowly decreased to cool down the material. The freedom of molecules to move is decreased with temperature. At the end, the energy of the material is minimal provided that the cooling speed was very slow.

The pseudo-code for Simulated Annealing is in Figure 12. An initial solution is created and in each iteration a random modification of the solution is allowed. Initially, at high temperatures, major modifications are allowed while as the temperature decreases smaller and smaller modifications are allowed. If a better solution than the previous is created, it is kept. And at a certain probability, in order to avoid local optimum, worse solutions are accepted.

```

Construct initial solution, x^{now};

Initial Temperature: T=TI;

while stop criteria not met do begin

for i = 1 to TL do begin

Generate randomly a neighboring solution x' \in N(x^{now});

Compute change of cost function \Delta C=C(x')-C(x^{now});

if \Delta C \le 0 then x^{now}=x'

else begin

Generate q = random(0, 1);

if q < e^{-\Delta C/T} then x^{now}=x'

end;

set new temperature T=\alpha \times T;

end;

Return solution corresponding to the minimum cost function;

```

Figure 12. Simulated Annealing algorithm.

#### 5.1.5 Genetic Algorithms

Genetic algorithm (pseudo-code in Figure 13) is inspired by nature and the theory of evolution [197]. An initial set of valid solutions called the population is created and in an iterative process, new solutions are created. The current population is replaced by a new population. In order to create a new solution, called a child, two solutions are selected, called parent1 and parent2. The selected parents create in a crossover process a child, which will belong to the new generation. The idea is that by combining features from the best solutions (selected parents) in current population, new better solutions (children) can be created. Each solution is creates a child solution. In order to avoid local optimum, mutation is allowed in the crossover process. A muta-

tion is, as in nature, the insertion of a small modification in the creation of the child solution.

```

Create an initial population pop

Do begin

newpop=empty

For i=1 to size_of_population Begin

parent1=select(pop)

child=crossover(parent1, parent2)

newpop=newpop+child

End

pop=newpop;

End;

Return solution corresponding to the minimum cost function;

```

Figure 13. Genetic algorithm.

## 5.1.6 Tabu Search

Tabu search is an optimization technique where the solution is improved through search in the neighborhood. An initial solution is created and a set of modifications are defined. The initial solution is through the defined modifications improved in n iterations. In order to avoid having a modification followed by a re-modification, a tabu list is used. The tabu list of length k keep track on the k last moved and prohibit cycles of length < k.

Chapter 3

# **Design for Test**

# **1 INTRODUCTION**

Design for testability is basically how to make each unit in the system testable. The intention with this chapter is to give an introduction to techniques for design for test. For further studies there are a number of books on test such as Abramovici *et al.* [2], Bushnell and Agrawall [24], Lala [151], Mourad and Zorian [199], Rajsuman [225] and Tsui [264].

Testing is used to check if a design is correct according to its specification. Failures can appear at any time during the life of a system, and a failure has occurred if the system's behavior is different from its specification. A *fault* is a physical defect that may or may not cause a failure, and a fault can be described by its nature, value, extent, and duration [151]. The nature of a fault can be logical or nonlogical. A logical fault makes the logic at a certain point in time different from its specification, while a nonlogical fault is due to the rest of the faults, such as clock signal distribution, power failure, etc. [151]. The value of a fault is simply how the fault creates the signal. The fault value can be fixed or it may vary over time. The extent of a fault is how the fault effect is distributed. A fault may affect only a part of the system, locally, or it can distribute over a larger part in the system. For instance, a logical fault may be local while a fault on the clock distribution is likely to be distributed through the system. The duration of the fault is if the fault is permanent or temporary. Sometimes a permanent fault is referred to as a hard fault and a temporary fault is a soft fault. A temporary fault or soft fault are often more complicated to replicate (make the fault appear again). These types of faults are due to not stable power supply (transient) or degradation (intermittent) [199].

Faults may appear in the system at any time. However, a majority of the faults, if any, are introduced during the manufacturing process. Hence, focus on production testing and on faults related to the manufacturing is of high importance.

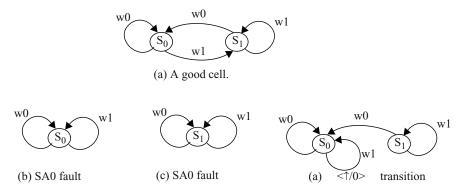

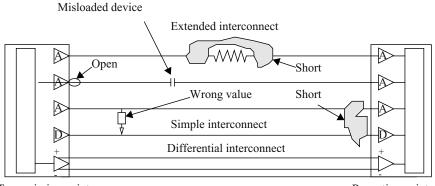

# 1.1 Fault models

The faults in a design can be due to defective parts, breaks in signal lines, lines unintentionally connected to ground or to the power supply, short-circuit between signal lines, and so on. Poor design may introduce faults such as hazards and races. A fault model is used to model the behavior of a fault. The most common fault models are the models for stuck-at faults (Section 1.1.1), bridging faults (Section 1.1.2), stuck-open fault (Section 1.1.3), and delay fault (Section 1.1.4).

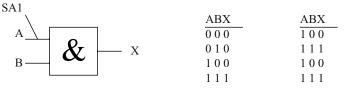

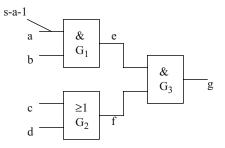

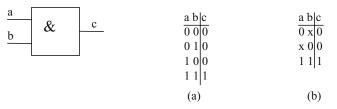

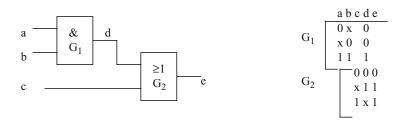

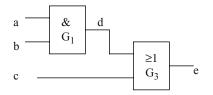

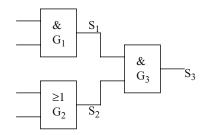

#### 1.1.1 Stuck-at Fault Model

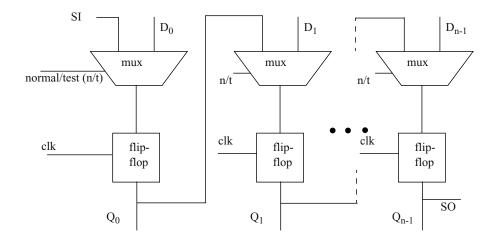

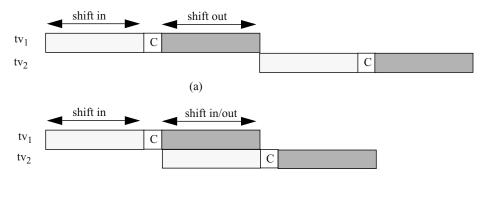

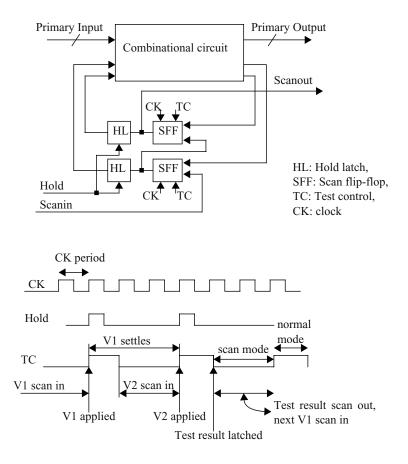

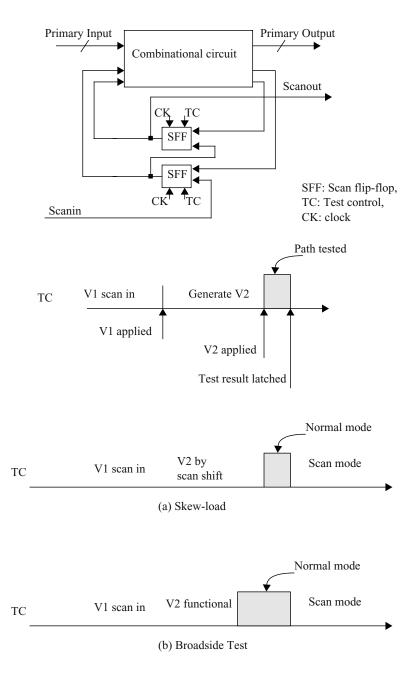

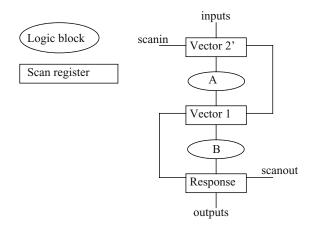

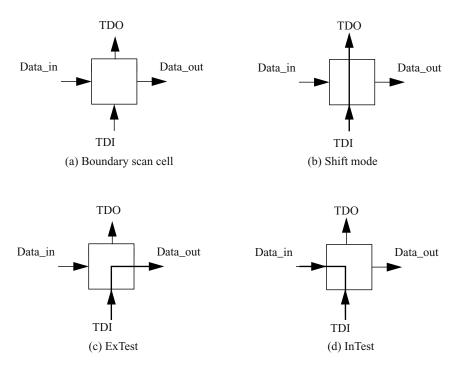

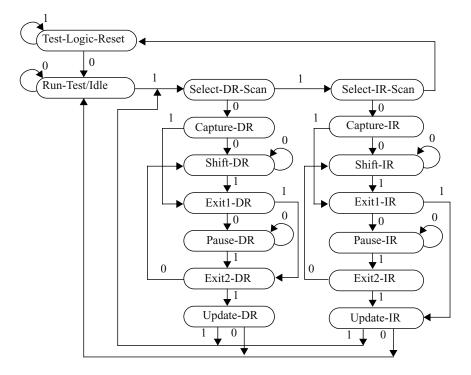

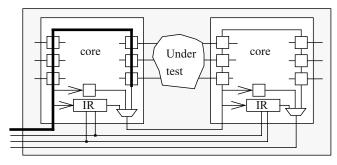

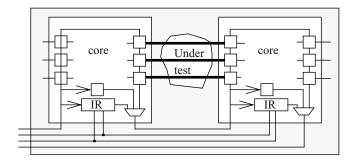

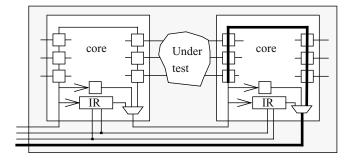

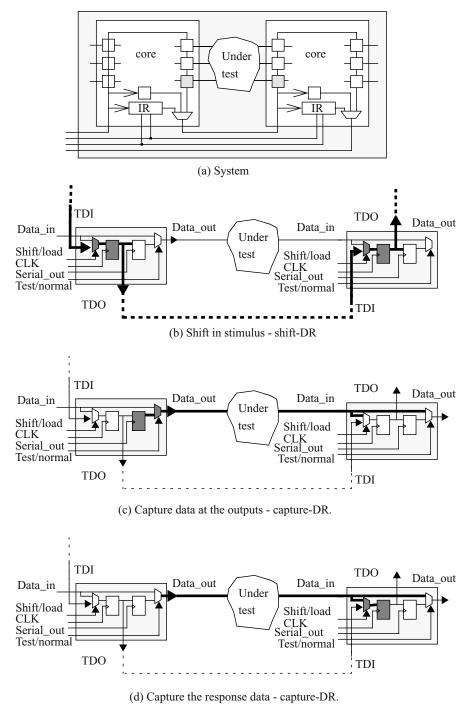

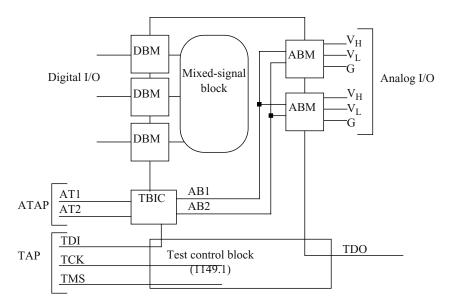

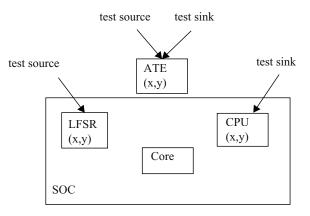

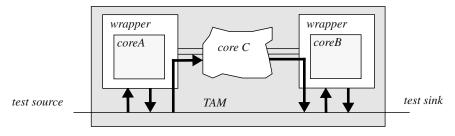

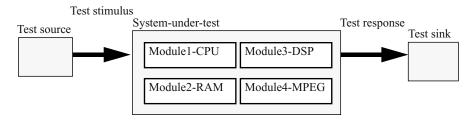

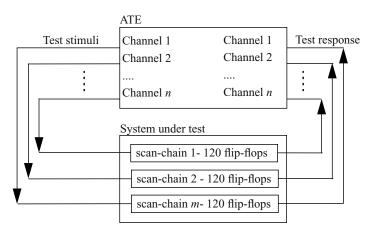

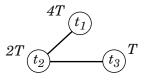

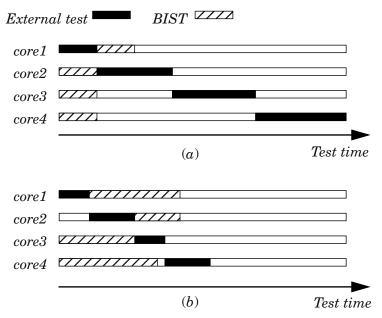

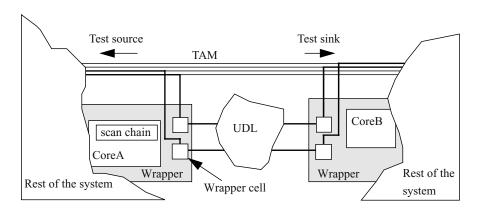

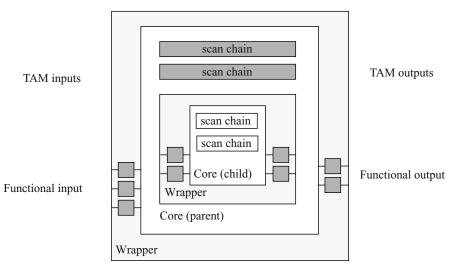

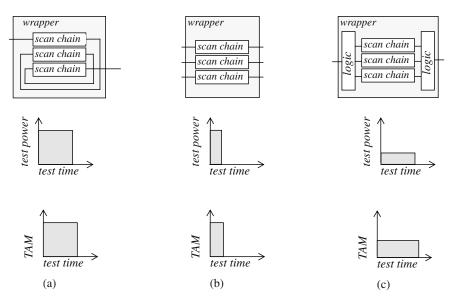

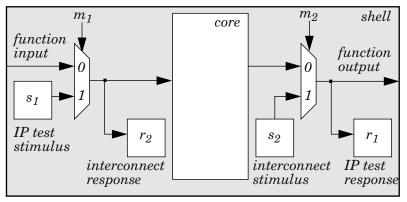

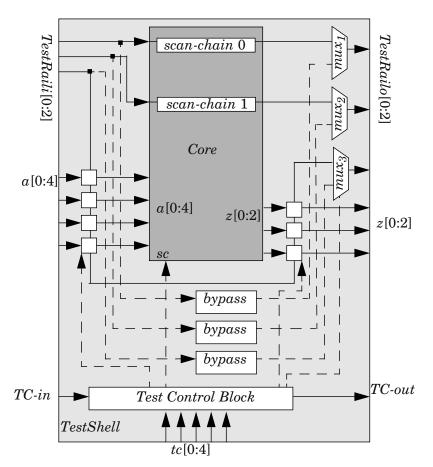

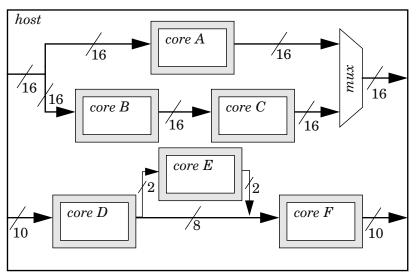

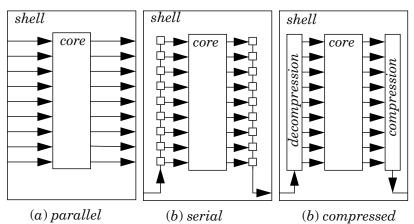

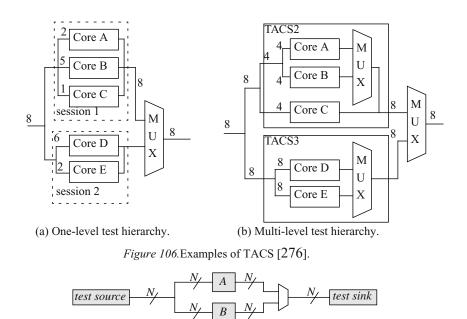

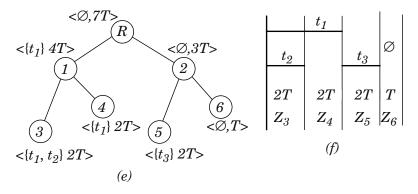

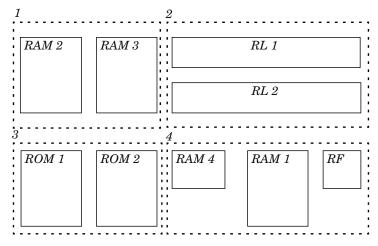

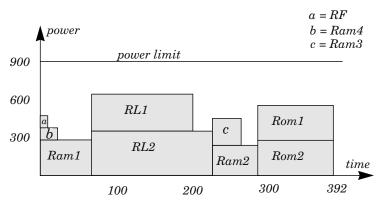

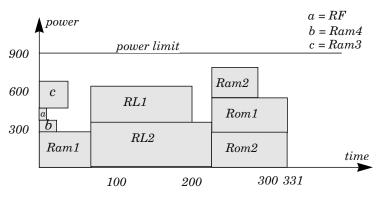

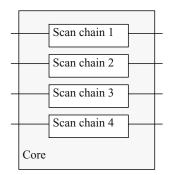

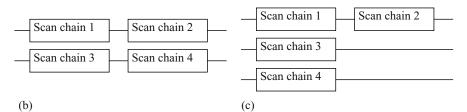

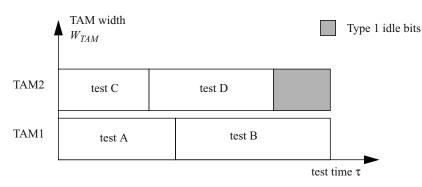

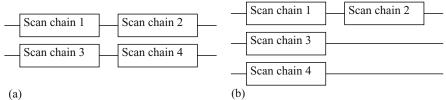

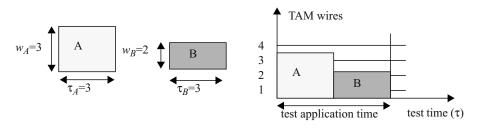

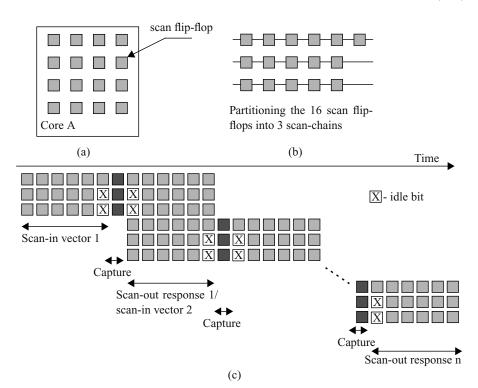

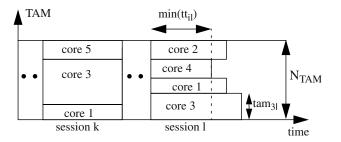

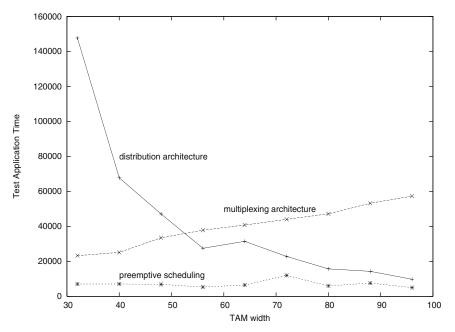

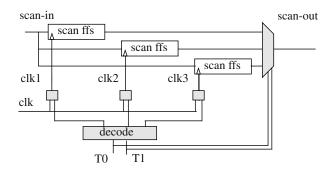

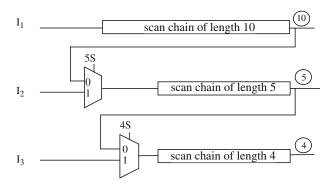

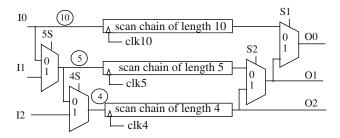

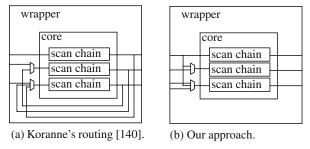

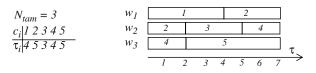

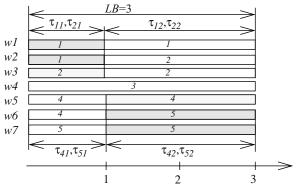

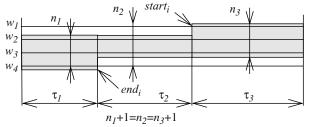

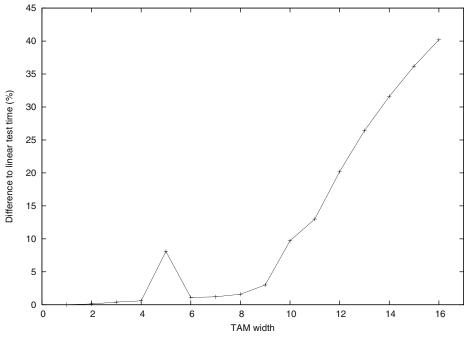

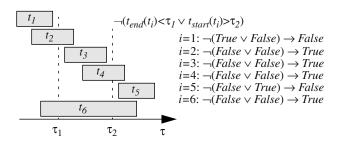

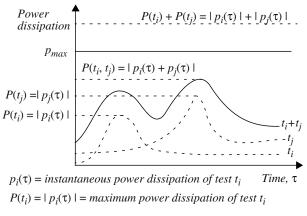

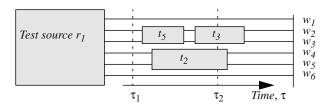

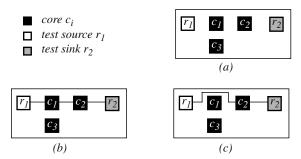

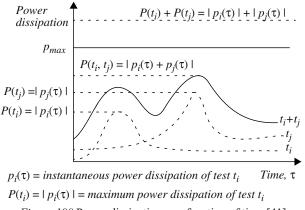

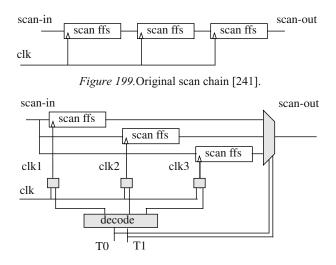

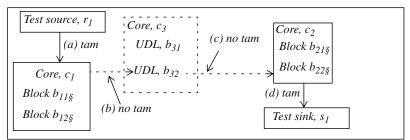

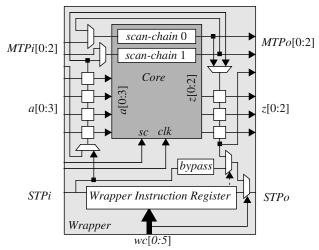

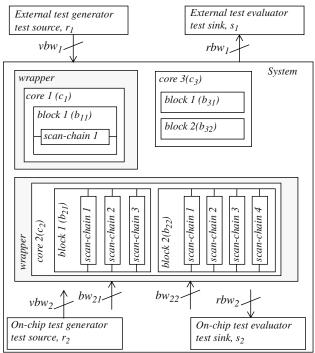

The most commonly used fault model is the single stuck-at (SSA) model. It assumes that a fault location can either be stuck-at 1 or stuck-at 0. If a fault at a wire is stuck-at 0, the logic value at the wire is always 0. In order to detect such a fault, the test stimulus should produce logic 1 at the wire. A stuck-at 0 fault at a wire is to be seen as if the wire is connected to ground. For a stuck-at 1, the wire acts as if it was connected to  $V_{dd}$  (power supply). For the generation of test vectors for SSA, it is assumed that only one fault appear in the system. Otherwise, if more than one fault is present at a time, the multiple stuck-at (MSA) fault model is used.